# CS 163 Logic Adder Lab Fall 2023

October 2, 2023

# Make sure to put the name of each team member on this sheet.

## 1 Overview

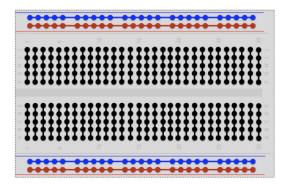

### 1.1 Breadboard Connections

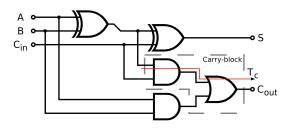

Figure 1 shows the electrical connectivity of a breadboard. Power buses on top and bottom of the board are labeled in blue and red. They are used to carry  $+5V (V_{cc})$  to the devices on your board. The internal circuit nodes (labeled in black) in rows of 5 pins.

### 1.2 Full Adder Circuit

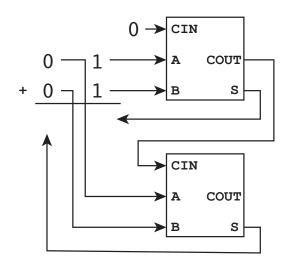

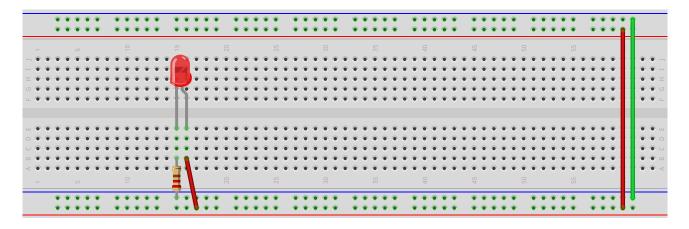

Figure 2 shows the logic circuit that implements a full adder. We will be building this logic circuit from discrete logic chips in this lab.

#### 1.2.1 7400 Series Logic Chips

We will use 7400 series logic chips in this lab to build the full adder.

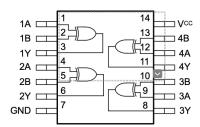

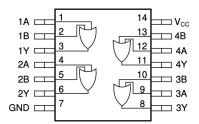

74HC86 Quad Exclusive OR The 74HC86 chip implements four exclusive OR gates on one chip. Figure 3a shows a pinout of the chip. The full chip datasheet is available on the COMP 163 course website.

The 74HC86, 74HC08, and 74HC32 each take a 5V power supply. They use 0V to represent a logic 0 and 5V to represent a logic 1.

Figure 1: Connectivity of a breadboard.

(a) Pinout of the 74HC86 quad exclusive OR gate.

(b) Pinout of the 74HC08 quad AND gate.

(c) Pinout of the 74HC32 quad OR gate.

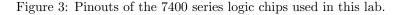

Figure 4: Test your power supply with an LED.

74HC08 Quad AND Gate The 74HC86 chip implements four AND gates on one chip. Figure 3b shows a pinout of the chip. The full chip datasheet is available on the COMP 163 course website.

74HC32 Quad OR Gate The 74HC86 chip implements four OR gates on one chip. Figure 3c shows a pinout of the chip. The full chip datasheet is available on the COMP 163 course website.

# 2 Procedure

### 2.1 Power Supply

You will start by building and testing the power supply on your breadboard. The power supply generates 5V power needed to run the 7400 series logic chips. Your breadboard will draw power from a USB cable that connects to your computer. It distributes 5V and GND to the breadboard's power rails, labeled with blue and green lines on the top and bottom

Figure 2: Logic circuit implementing a full adder.

of the breadboard (shown in Figure 1). The output pins of the power supply are labelled VCC and GND (for +5V and  $GND^{1}$ ).

To test your power supply, connect the positive terminal of an LED to +5V. Connect the LED's negative terminal through a 100 $\Omega$  resister to ground. Figure 4 shows the test configuration. If your power supply is working, the LED should light up.

### 2.2 Placing Logic Chips

Place your 7400 series logic chips on your breadboard as shown in Figure 5. On each chip, connect the  $V_{CC}$  pin to your +5V bus and GND pin to your GND bus.

### 2.3 Full Adder Sum

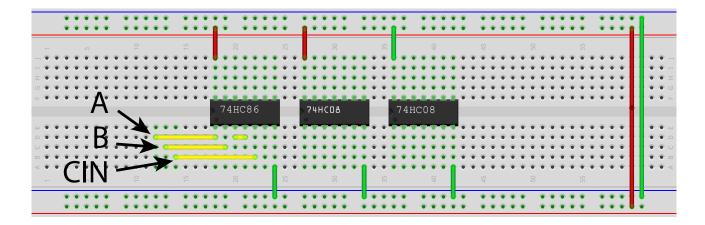

Next, build the sum circuit, which generates the S output of the full adder. The sum circuit consists of two XOR gates (Figure 2) that XOR the A, B, and CIN inputs together. Figure 6 shows the circuit connected on the 74HC86

$<sup>^1{\</sup>rm GND}$  is the same as 0V.

|      |     | • • |            | C   | •   |   | ۲ | • | • | •   | •   | 1   | • • | 3   | •   | ۲  |    | •  | •   | • • |     | •   | ۲   | ٠   | •   | • • |   | • ( | • • | ۲ | ۲   |     | •  | •   | • • |   | • | • • | •   | • |    | • • | • • |     | • |   | • • |      | • | 1 |   |   |

|------|-----|-----|------------|-----|-----|---|---|---|---|-----|-----|-----|-----|-----|-----|----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|---|-----|-----|---|-----|-----|----|-----|-----|---|---|-----|-----|---|----|-----|-----|-----|---|---|-----|------|---|---|---|---|

|      | 1   | • • | • •        | 2.5 | •   |   | ۲ | • | • | •   | •   | 1   | • • | 2.3 | 1   | ۲  |    | •  | •   | • • |     | •   | 1   | ۲   | •   | • • | ) | • 1 | • • | 1 | ۰   | ۲   | •  | •   | • • |   | • | • • | • • | • |    | • • | • • | • • | • |   | • • | 2.0  |   | 1 |   | _ |

|      |     |     |            |     |     |   |   |   |   |     |     |     |     |     |     |    |    |    |     |     |     |     | T   |     |     |     |   |     |     | I |     |     |    |     |     |   |   |     |     |   |    |     |     |     |   |   |     |      | I | Т |   |   |

| • •  | •   | • • | • 4        | . 4 |     | ۲ | ۲ | • | • | •   | • ( | •   | • • | 6.4 | - 5 | ۲  | ۲  | •  | •   | • • |     | •   |     | ٠   | •   | • • | ٠ | •   |     | U | •   | • • | •  | •   | • • | ۲ | • | • • |     | ۲ | •  | • • | • • |     | ۲ | • | • • | P 4  |   |   | ۲ |   |

| Ð (  | • ( | • • | Ð (        | 6   | •   | ۲ | ۲ | • | • | •   | • ( | • ( | • • | 6.4 | •   | ۲  | ۲  | •  | •   | • • | •   | •   | ۲   | ۲   | •   | • • | ۲ | • ( | • • | ۲ | ٠   | • • | ۲  | •   | • • | ۲ | • | • • | • • | ۲ | ٠  | • 4 | • 4 | • • | ۲ | ٠ | • • | P (4 |   |   | ۲ |   |

| Ð (  | • ( | • • | • 1        | 9.4 | •   | ۲ | ۲ | • | • | • ( | • 1 | • ( | • • | 6.4 | •   | ۲  | ۲  | •  | •   | • • | •   | •   | ۲   | ۲   | •   | • • | ۲ | • ( | • • | ۲ | ۲   | • • | •  | • ( | • • | ۲ | ٠ | • • | • • | ۲ | ٠  | • • | • • | • • | ۲ | ٠ | • • |      |   |   | ۲ |   |

| P (  | •   | • • | • 1        | 9   |     |   | • | • | • | •   | • 1 | • 1 | • • | 9.9 | •   | ۲  | ٠  | •  | • 1 | • • | •   | •   | ۰   | ٠   | •   | • • | • | • 1 | ••• | ٠ | •   | • • | •  | •   | • • |   | • | • • |     |   | •  | • • | • • | •   |   | • | • • | •    |   |   | ٠ |   |

| • •  | • 1 | • • | <b>F</b> ( | 6.4 |     |   | • | • | • | • : | • 1 | • 1 | • • | 5.4 | 1   | 2  | 2  | -  |     | - 1 | 5   | • • |     | *   |     |     |   | •   | • • | * | -   |     | -  | **  | •   |   | • | • • |     | • | •  | • • | • • |     | • | • | • • |      |   | Т | ۰ |   |

|      |     |     |            |     |     |   |   |   |   |     |     |     |     |     |     | 74 | НC | :8 | 6   |     |     |     | ) ī | 741 | HCC | )日  |   |     |     |   | 741 | HC  | 36 |     |     |   |   |     |     |   |    |     |     |     |   |   |     |      | 1 |   |   |   |

| р. 4 | •   | • • |            |     |     |   | • | • | • | •   | • • | •   | • • |     |     |    |    |    |     |     | 2.4 |     | -   |     |     |     |   | -   |     | - |     |     |    |     | • • |   | • | • • |     |   | ÷. | • • | • • |     |   | • | • • |      |   |   |   |   |

| . 4  | •   | • 4 |            | . 4 |     |   | ÷ | • | • | •   | • ( | • • | • 4 | . 4 |     | ۲  | ٠  | •  | •   | • • |     | •   |     | ۲   | •   | • • | • | •   |     | ٠ |     | • • | •  | •   | • • |   | • | • • |     |   | •  | • • | . 4 |     |   | • | • • |      |   |   |   |   |

| 6.4  | •   | • • | • 4        |     |     | ٠ | ۲ | • | • | •   | • ( | • ( | • • | 6.4 | •   | ۲  | ٠  | •  | •   | • • |     | •   | ۲   | ۲   | •   | • • | ۲ | •   | • • | ۲ | •   | • • | •  | •   | • • | ۲ | • | • • |     | ۲ | •  | • 4 | • • |     | ۲ | ٠ | • • |      |   | ÷ | ۲ |   |

| 6.4  | • ( | • • | Ð (        | 6.4 | •   | ۲ | ۲ | • | • | •   | • 1 | • 1 | • 4 | 6.4 | •   | ۲  | ۲  | •  | •   | • • | •   | •   | ۲   | ٠   | •   | • • | ۲ | ٠   | • • | ۲ | ٠   | • • | •  | • ( | • • | ۲ | • | • • | • • | ۲ | ٠  | • 4 | • 4 | • • | ۲ | ٠ | • • | 6.4  |   |   | ۲ |   |

| Ð (  | • ( | • • | Ð (        | 6.4 | • • | ۲ | ۲ | • | • | • ( | • ( | • ( | • • | 6.4 | •   | ۲  | ۲  | •  | • ( | • 1 | 1.4 | •   | ۲   | ۰   | •   | • • | ۲ | 14  | • • | ۲ | ۲   | • • | •  | •   | •   | ۲ | • | • • |     | ۲ | ٠  | • • | • • | • • | ۲ | ٠ | • • |      |   |   | ۲ |   |

|      |     |     |            |     |     |   |   |   |   |     |     |     |     |     |     |    |    |    |     |     | 5   |     |     |     |     |     |   |     |     |   |     |     |    |     |     |   |   |     |     |   |    |     |     |     |   |   |     |      |   |   |   |   |

| _    | _   |     |            |     |     | _ | - | - | - | -   |     |     |     |     |     | -  | _  | -  |     | _   |     | _   | -   | -   | -   |     | _ |     |     | - | -   | _   |    | -   |     | _ | - |     |     | - | _  | -   |     |     | - |   | -   |      |   |   | _ | 1 |

|      |     |     |            | Č.  |     |   |   |   |   | •   | •   |     |     |     |     |    |    |    | •   | •   |     |     |     |     |     |     |   |     |     |   |     |     |    |     |     |   |   | •   |     |   |    | •   |     |     |   |   | •   |      |   | 2 |   |   |

|      |     | • • | • •        |     |     |   | ۰ | • | • | •   | •   | 1   | • • |     | • • | ۰  |    | •  | •   | • • |     |     | ٠   | ۰   | •   | • • |   | •   | • • | ۰ | ٠   |     | •  | •   | • • |   | • | • • |     | • |    | • • | • • |     | • |   | • • |      |   | ۰ |   |   |

Figure 5: Logic chips placed on the breadboard.

Figure 6: The sum circuit.

XOR chip.

The A and B inputs to the full adder go in to the chip's first XOR gate on pins 1 and 2. The output of the first XOR gate (pin 3) goes in to the input of the second XOR gate on pin 4. Pin 5 (the second input of the second gate) comes from the CIN input signal. The output of the second gate (pin 6) generates the sum output signal.

To test this circuit, connect the S output from pin 6 on the 74HC86 through an LED and a resistor to GND. Use the same LED configuration as the power supply test, but supply power to the LED from the output of the XOR gate instead of from the power supply on the board. Connect the A, B, and CIN signals to +5V power supply or GND. Test different combinations of +5V and GND on the A, B, and CIN inputs to see when the LED lights up. Record the results in Table 1.

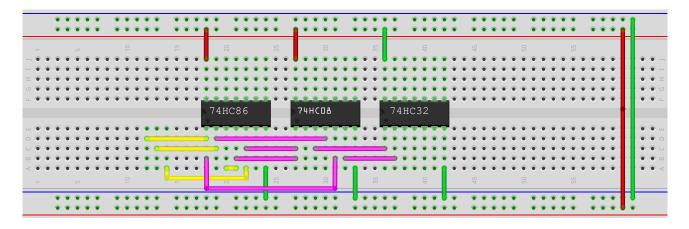

### 2.4 Building the Carry Logic

Next, build the carry logic for your full adder. Carry logic consists of two AND gates and one OR gate. Figure 7 shows the carry logic in pink wires. The output of the OR gate on pin 3 of the 74HC32 is the full adder's COUT signal.

Test your carry out logic the same way you tested your sum logic. Hook

Table 1: Sum Output of Full Adder

| А  | В  | CIN | LED |

|----|----|-----|-----|

| 0V | 0V | 0V  |     |

| 5V | 0V | 0V  |     |

| 5V | 5V | 0V  |     |

| 5V | 5V | 5V  |     |

Figure 7: The full adder, including carry logic

up the A, B, and CIN inputs to +5V or GND. Connect the S output to an

LED and COUT output to a second LED. Record the state of the S and COUT LEDs for different input configurations in Table 2.

Once your group gets the carry logic working, demo to your instructor.

Table 2: Sum & Carry Output of Full Adder

#### 2.5 2-Bit Adder

The full adder we built can add two 1-bit numbers together. To add 2-bit numbers together, we need to build a second full adder and connect it to the first one we built. A schematic of the 2-bit adder is shown in Figure 8. In the schematic, the two full adders are shown as blocks with their inputs and outputs. Inside each block is the logic from Figure 2.

In this section, you will build a second full adder using the same procedure as you used to build the first. You can use extra gates on your logic chips. As shown in Figure 8, you will connect the carry out from the first full adder to the carry in of the second full adder.

I will not provide breadboard diagrams for the second full adder—you need to figure out the connections on your own. You can use the pinout diagrams in Figure 3.

When you have completed the 2-bit adder circuit, demo to your instructor.

| А  | В  | CIN | COUT LED | S LED |

|----|----|-----|----------|-------|

| 0V | 0V | 0V  |          |       |

| 5V | 0V | 0V  |          |       |

| 5V | 5V | 0V  |          |       |

| 5V | 5V | 5V  |          |       |